Member-only story

Fundamentals of High-Level Synthesis Part 2: Concurrency vs Parallelism

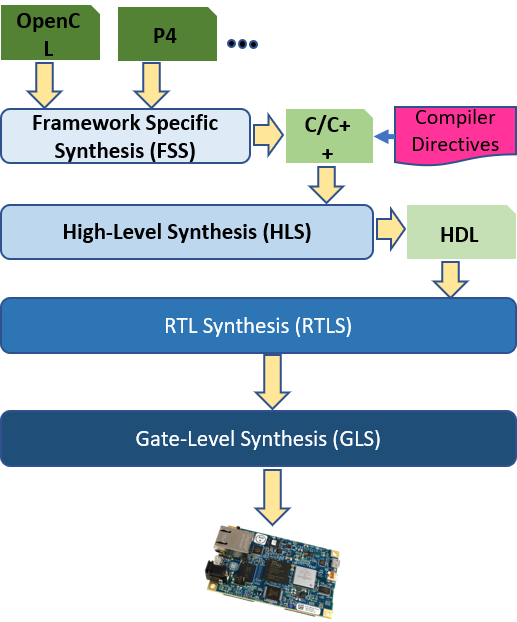

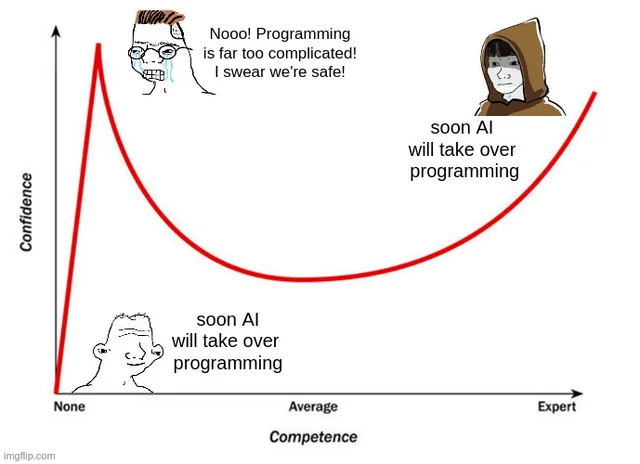

Concurrency and parallelism are two main concepts in high-level synthesis (HLS) design flow that their understanding is crucial in implementing an algorithm efficiently on FPGAs.

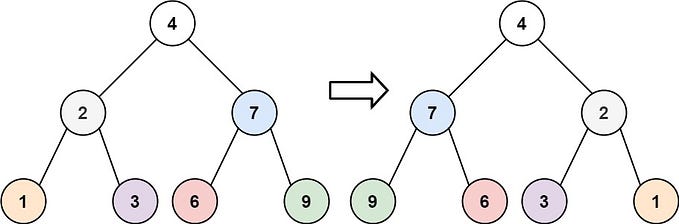

Whereas the concurrency is a concept at the level of algorithm, parallelism is a hardware-dependent concept. For example, Let’s consider the two L1 and L2 for-loops in the following snippet code. As there is not any data or control dependency between them, they are concurrent and potentially can be executed in parallel. However, their parallel execution depends on the underlying computational platform.

L1:for (int i=0; i < N; i++)

c[i]= a[i]+b[i]

L2:for (int j=0; j < M; j++)

d[j]= e[j]*f[j]If there is only one ALU to perform the addition and multiplication, then these loops should be executed sequentially one after the other or their iterations can be interleaved and run serially. If there is more ALUs available, then the two loops can be performed in parallel. Therefore, the amount of parallelism extracted from a concurrent code depends on the underlying hardware resources. Note that as loop iterations are independent, the concurrency can also be explored among the iterations of each loop. The interested reader can think about different cases of parallelism in implementing the loop…